Then, we declare a new array type that can hold two such BCD values. Type digits_type is array (1 downto 0) of digit_type Īs shown in the code above, we declare a subtype of the integer on the range 0 to 9 for describing the value that can be represented by one decimal digit. Subtype digit_type is integer range 0 to 9 We can’t distinguish between the decimal digits merely by slicing the vector used to store the number.

While a binary representation is the most efficient way to store the decimal number, we run into problems when trying to split it into the left and right digit to show on the display.

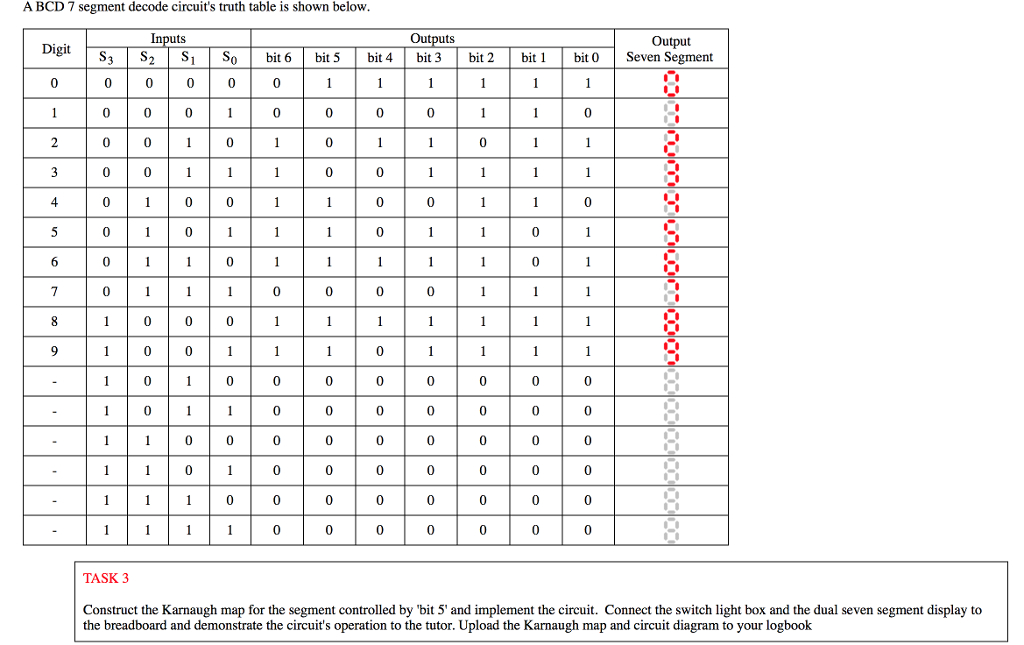

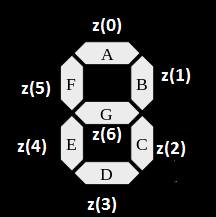

To represent the digits shown on the display we will use the format known as binary-coded decimal (BCD). The output signals are the seven segments as a vector and the digit selector signal for picking either the left or the right digit to illuminate. The value signal is an integer type restricted to the range 0 to 99 because these are the only number values it’s possible to show using only two digits. In addition to the clock and reset, the entity has one input signal: the value to display on the 7-segment display. Segments : out std_logic_vector(6 downto 0) refresh_hz = (2 ** clk_cnt_bits) / clk_hz The formula that determines the refresh rate is refresh_hz = 2 clk_cnt_bits / clk_hz. Select a counter length that lies in the range from 50 to a couple of hundred Hertz. It defines the length of an internal counter that controls the refresh rate of the display, the frequency of alternating between the left and right digits. The entity has a generic port with a constant named clk_cnt_bits. The code below shows the entity of our seg7 VHDL module. The “DP” decimal point is unconnected and cannot be accessed.

When the logic voltage on this pin is '0', the right digit illuminates, if it’s '1', the left digit is activated. The P4/C pin on the J2 connector selects one or the other digit. But there are two digits on this display, and we can only control one at the time. By driving a logic high value on such a pin, the corresponding segment will illuminate on the display. Seven of the pins control one segment each on the display. These pins are directly accessible to the FPGA on the iCEstick. It shows how the 7-segment display connects to the Pmod pins. The image above is from the datasheet for the Digilent Pmod module. However, you can use the code presented in this article as a basis and modify it to suit your needs. A generic solution that covers all possible 7-segment displays that you may encounter probably wouldn’t be very user-friendly. The number of digits varies between them, and so does the physical interface and pinout. There are many different 7-segment displays on the market. Finally, I recommend getting a USB type-A extension cable because plugging the iCEstick directly into the USB port on the computer is impractical. In addition to the iCEstick, you need a 2×6-pin to Dual 6-pin Pmod Splitter Cable to convert from the parallel Pmod connector on the iCEstick to the in-series version of the plug that the 7-segment display expects. To test the VHDL implementation, I’m using the Lattice iCEstick, a low-cost FPGA development board with a Pmod connector. It fits into the Pmod connector, which is standard on many FPGA development boards. The dual 7-segment display is compatible with the Pmod interface, meaning that you can use it without any soldering. In this article, I will present a VHDL module that can display a two-digit number on the Pmod SSD: Seven-segment Display from Digilent.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed